Project I Have Made with Group

A clear, concise overview highlighting the essence of your work

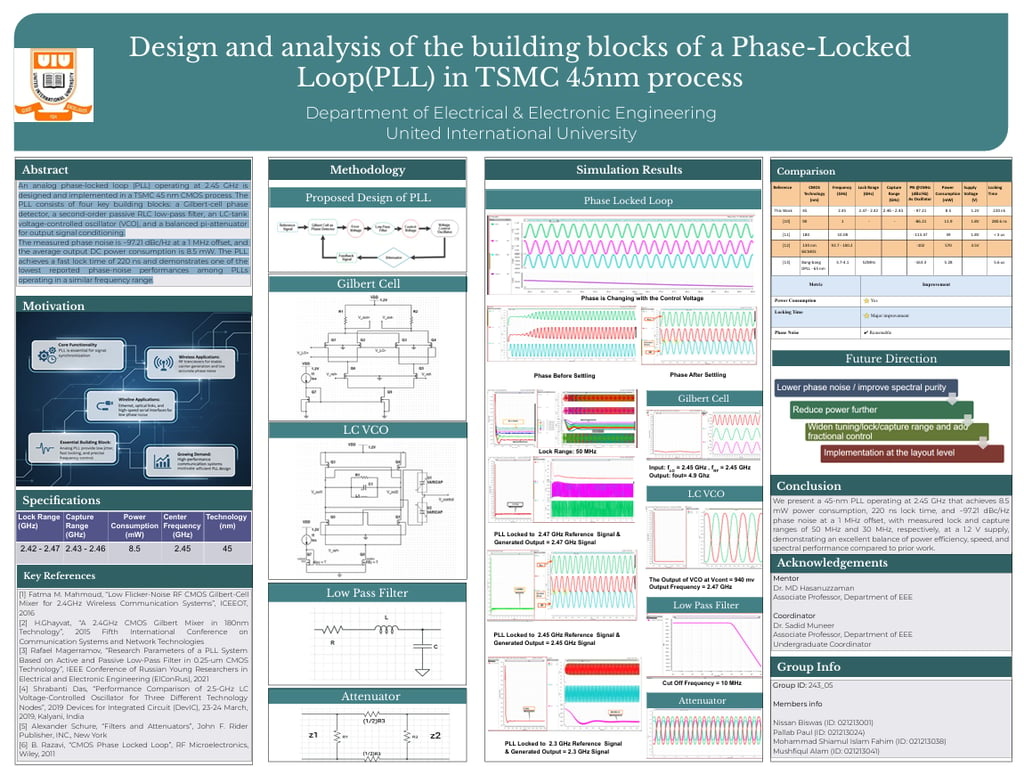

Design and analysis of the building blocks of a Phase-Locked Loop (PLL) in TSMC 45nm process

Abstract

An analog phase-locked loop (PLL) operating at 2.45 GHz is designed and implemented in a TSMC 45 nm CMOS process. The PLL consists of four key building blocks: a Gilbert-cell phase detector, a second-order passive RLC low-pass filter, an LC-tank voltage-controlled oscillator (VCO), and a balanced pi-attenuator for output signal conditioning. The measured phase noise is −97.21 dBc/Hz at a 1 MHz offset, and the average output DC power consumption is 8.5 mW. The PLL achieves a fast lock time of 220 ns and demonstrates one of the lowest reported phase-noise performances among PLLs operating in a similar frequency range.

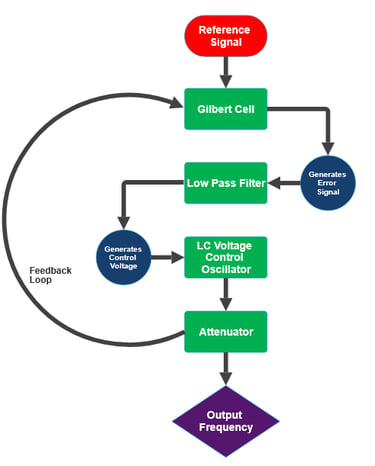

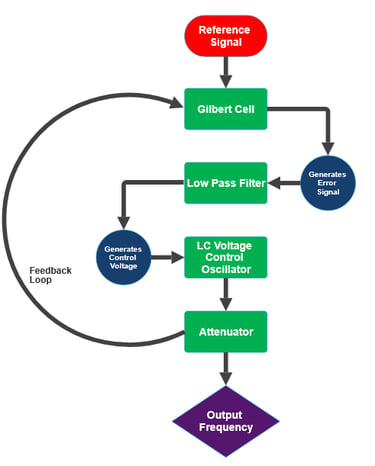

Blocks of PLL

Flow Diagram of the Working Process of PLL

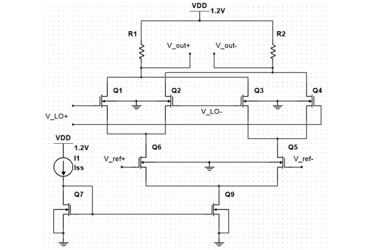

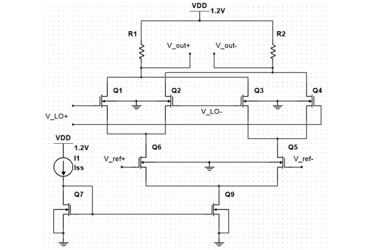

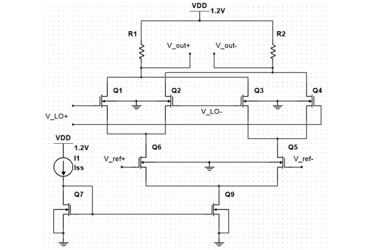

Gilbert Cell as Phase Detector

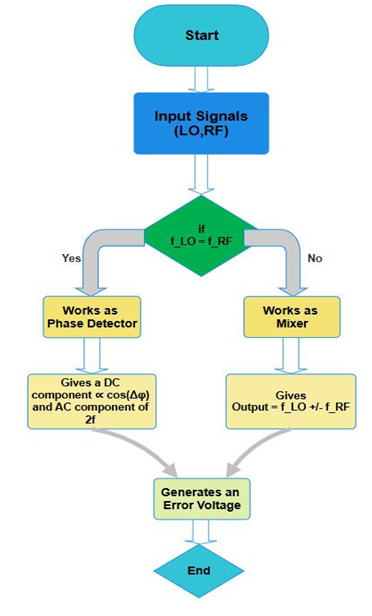

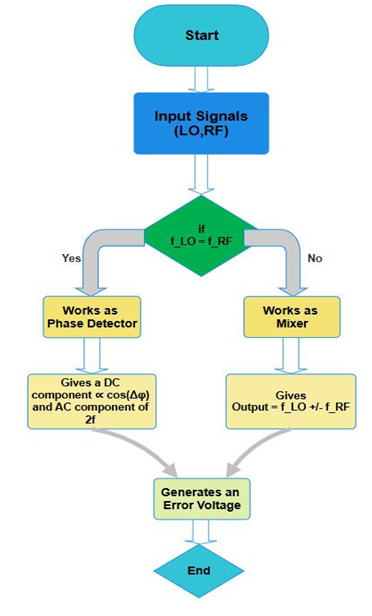

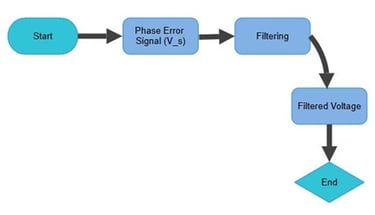

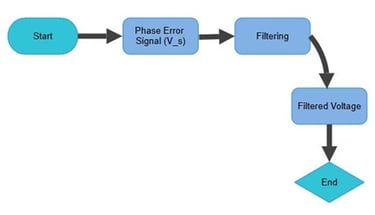

Work Flow Diagram Gilbert Cell as Phase Detector

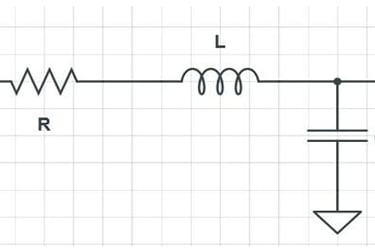

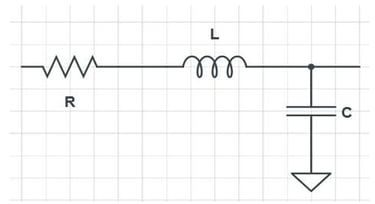

Low Pass Filter

LC Voltage Controlled Oscillator (VCO)

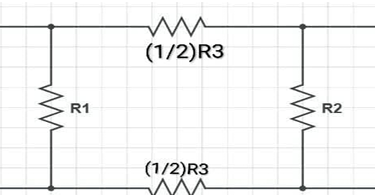

Attenuator

Work Flow Diagram Low Pass Filter

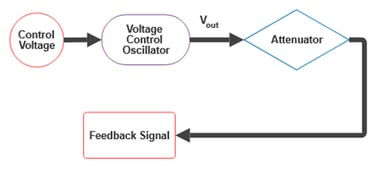

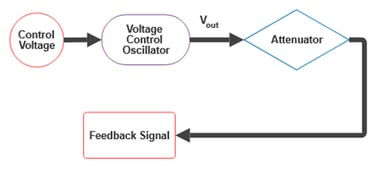

Work Flow Diagram Voltage Controlled Oscillator

Design and Outcome of PLL

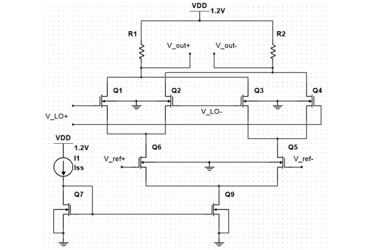

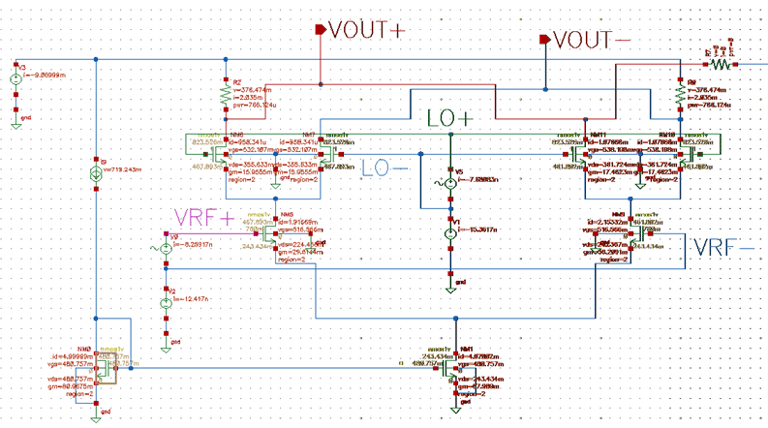

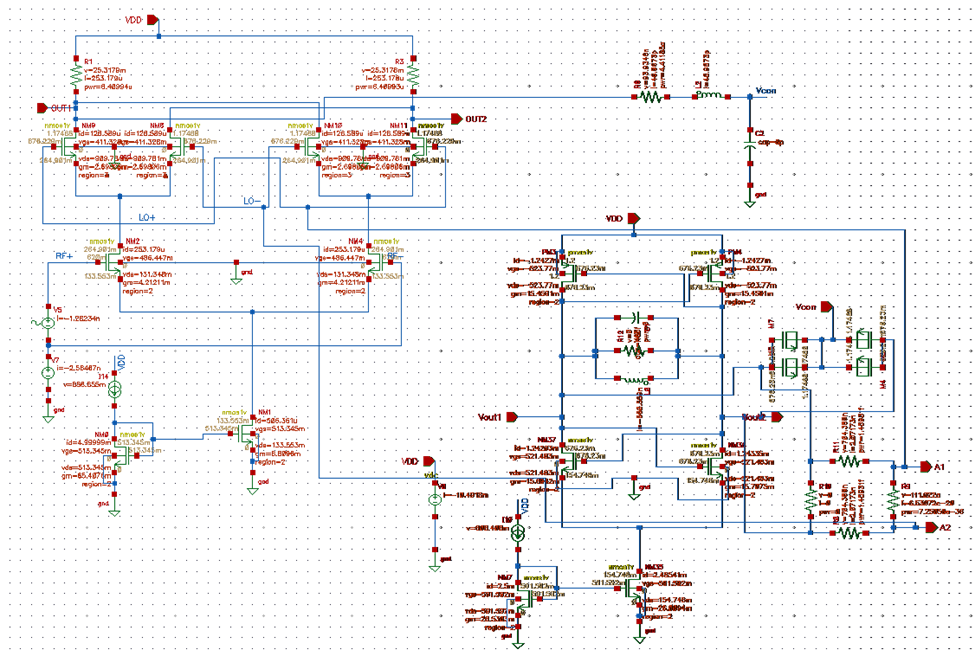

Schematic Design of Gilbert Cell as Phase Detector

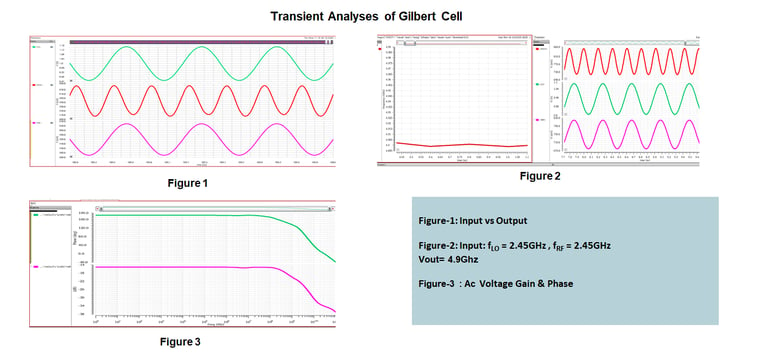

Outcome of Gilbert Cell as Phase Detector

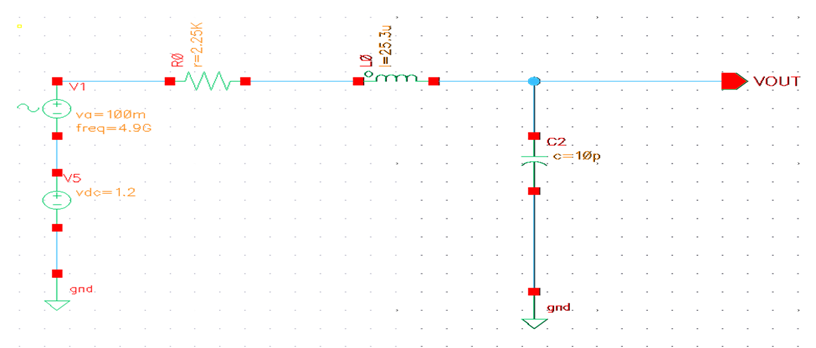

Schematic Design of 2nd Order Low Pass Filter

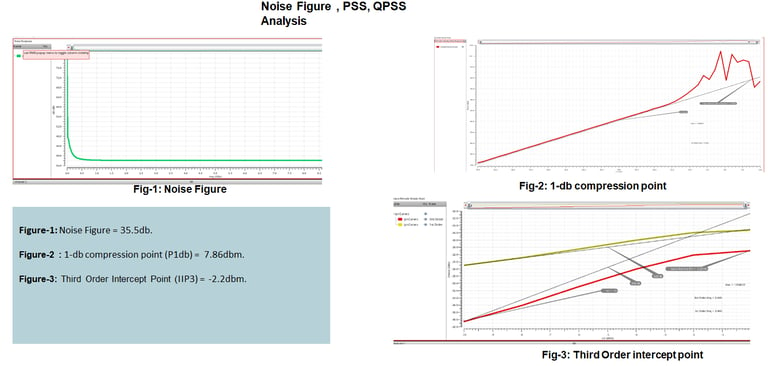

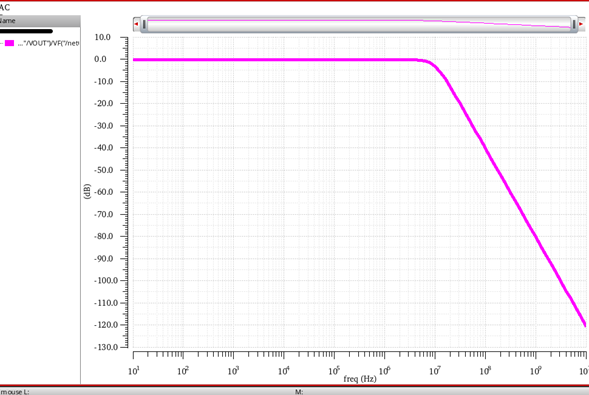

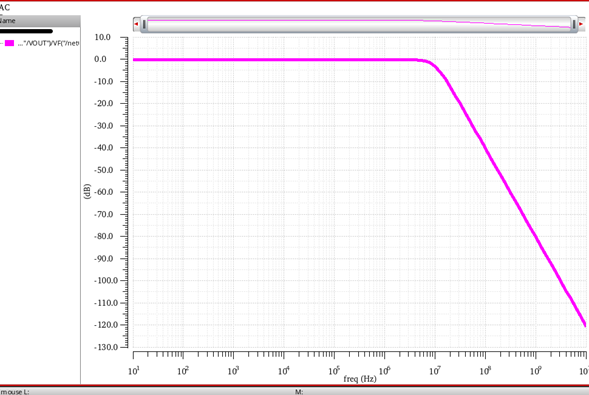

Outcome of 2nd Order Low Pass Filter

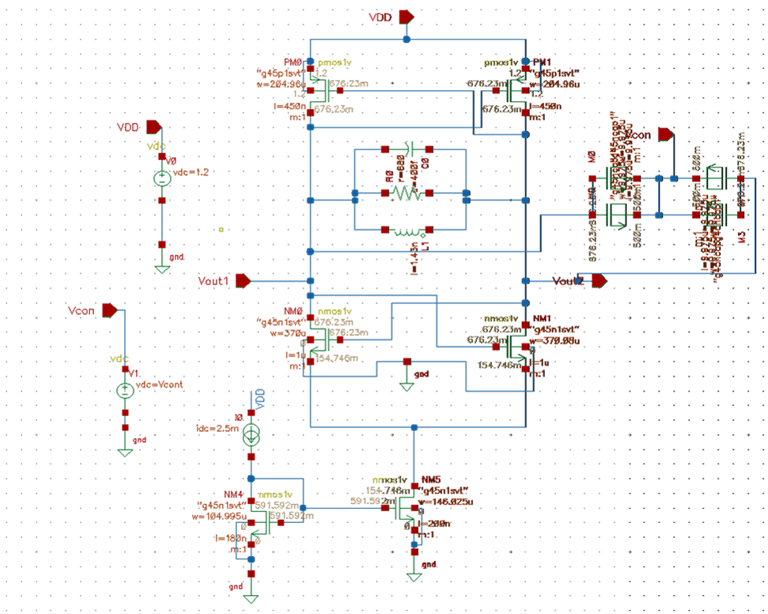

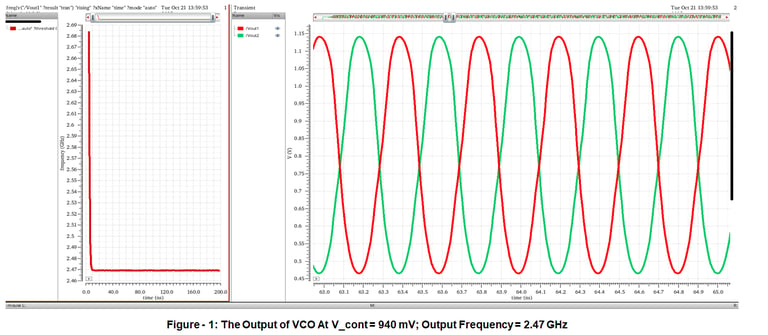

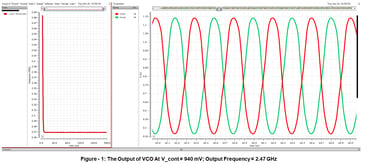

Schematic Design of LC Voltage Controlled Oscillator (VCO)

Outcome of LC Voltage Controlled Oscillator (VCO)

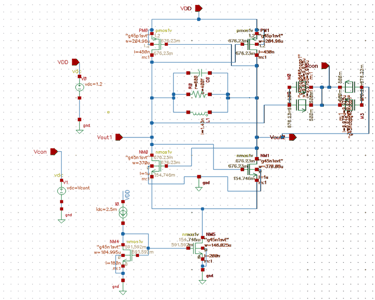

Schematic Design of Complete Phase Locked Loop (PLL)

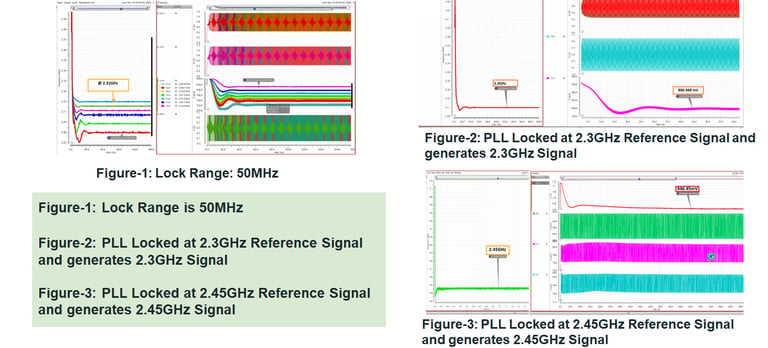

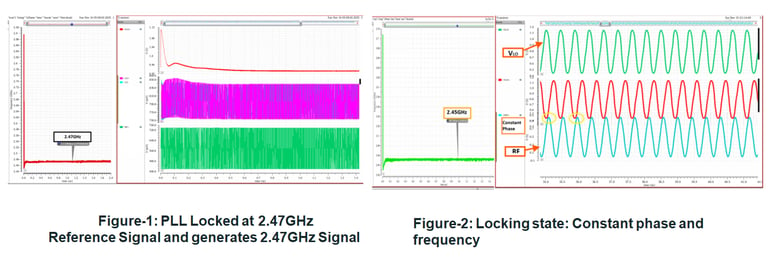

Outcome of Complete Phase Locked Loop (PLL)

Team Members

Nissan Biswas (ID No. 021 213 001)

Linkedin Account: Nissan Biswas

Pallab Paul (ID No. 021 213 024)

Linkedin Account: Pallab Paul

Mohammad Shiamul Islam Fahim (ID No. 021 213 038)

Linkedin Account: Mohammad Shiamul Islam Fahim

Mushfiqul Alam (ID No. 021 213 041)

Acknowledge To

Dr. Md. Hasanuzzaman

Associate Professor, Dept. of EEE

Email: hasanuzzaman@eee.uiu.ac.bd

I would like to express my sincere gratitude to my mentor, Dr. Md. Hasanuzzaman (Associate Professor, Dept. of EEE), for his continuous guidance, support, and valuable insights throughout my work.

Dr. Kaled Masukur Rahman

Professor, Dept. of EEE & Head of Dept.

Email: masuk@eee.uiu.ac.bd

I am also thankful to the coordinator of Capstone Project 1, Dr. Kaled Masukur Rahman (Professor, Dept. of EEE & Head of Department), for his direction and encouragement during the project.

Dr. Sadid Muneer

Associate Professor, Dept. of EEE & Undergraduate Coordinator

Email: sadidmuneer@eee.uiu.ac.bd

Additionally, I would like to acknowledge the coordinator of Capstone Project 3, Dr. Sadid Muneer (Associate Professor, Dept. of EEE & Undergraduate Coordinator), for his support and supervision.